Doctoral students Xinyue Wu and Ruge Xu from the University of Michigan-Shanghai Jiao Tong University Joint Institute (UM-SJTU JI, JI hereafter) have secured second place finish in the finals of the China Computer Federation (CCF) Chip Conference’s special competition. The competition, known as the “CCF-DAC: ASIC DRC Violation Prediction Model Design and AI-PC Deployment Challenge,” is a highly respected event within the field of integrated circuit design.

Xinyue Wu (first on the left) receives the award certificate of the competition on the stage.

Under the guidance of JI Professor Xinfei Guo from the Intelligent Circuits, Architectures, and Systems (iCAS) Lab, the team competed against participants from leading institutions, including Peking University, Huazhong University of Science and Technology, and Tongji University. The competition attracted multiple teams, with the finalist groups composed entirely of Ph.D. students.

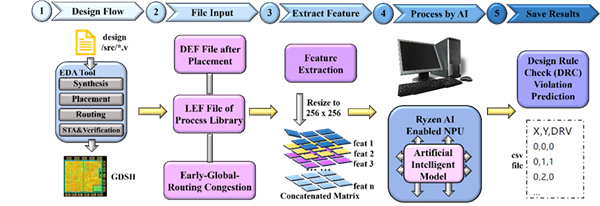

The CCF Chip 2024 event featured two main competition tracks: AI4EDA and LLM deployment on consumer-grade graphics cards. These challenges aim to advance the fields of integrated circuit Electronic Design Automation (EDA), hardware-software co-design, and AI application. The CCF-DAC Challenge is designed to promote the use of AI in ASIC EDA algorithms, particularly focusing on the deployment of these algorithms on AI-PC platforms to improve computational efficiency.

Diagram of the event procedure of the competition

In the ASIC chip design and verification process, predicting and resolving Design Rule Check (DRC) violations is a critical task. DRC ensures that chip layouts and wiring adhere to manufacturing process requirements. As chip designs become more complex and manufacturing processes advance, the complexity of DRC increases, leading to extended verification cycles and higher production costs. Early identification and resolution of potential DRC violations are essential for efficient chip design.

AI technology plays a significant role in addressing these challenges. By analyzing large datasets of historical design information and corresponding DRC outcomes, AI models can be developed to predict potential violations in new designs. This approach can streamline the design verification process, reduce costs, and improve chip production quality.

Final defense presentation of CCF Chip Conference

Reflecting on the competition, team leader Xinyue Wu expressed her gratitude for the collaborative spirit within the team. “I am particularly grateful to every member of our team. Throughout the competition, we trusted and supported each other, overcoming numerous challenges together,” Wu said. She also highlighted the invaluable learning opportunities the competition provided, which broadened her technical knowledge and fostered connections with peers from other institutions working on similar research.

Student Introduction

Xinyue Wu

Xinyue Wu is a JI doctoral student in the 2024 cohort. She has previously received honors such as the second prize in the “TI Cup” Shanghai University Student Electronic Design Competition. Her current research focuses on electronic design automation prediction problems based on machine learning.

Ruge Xu

Ruge Xu is a JI doctoral student in the 2023 cohort. She completed her undergraduate studies at Shanghai Jiao Tong University and earned her master’s degree from the School of Information at the University of Michigan. Xu has received honors such as the JI Development Scholarship and the Outstanding Graduate Award. Her current research focuses on hardware-software co-design, edge AI, and model quantization.

Advisor Introduction

Xinfei Guo

Xinfei Guo is a tenure-track associate professor at JI. He is a senior member of IEEE, ACM and CCF. He received his Ph.D. in Computer Engineering from the University of Virginia. He also holds a Master’s degree in Electrical and Computer Engineering from the University of Florida. Before joining JI, he worked at Nvidia and IBM research in US, where he served as a key member to contribute to multiple chip products. His previous work has results in over 50 conference or journal papers in IC design, EDA or FPGA fields. He also published a book and holds three patents. Currently, he serves as Associate Editor-in-Chief for IEEE Transactions on Very Large Scale Integration Systems, Associate Editor for Integration, the VLSI Journal, and PC member or chair positions for over 30 international conferences, such as DAC, CICC, ICCAD, ASPDAC, FCCM, HOST and more. His team currently focuses on low-power and high-reliability computing, machine learning-assisted EDA techniques and reconfigurable computing architectures.