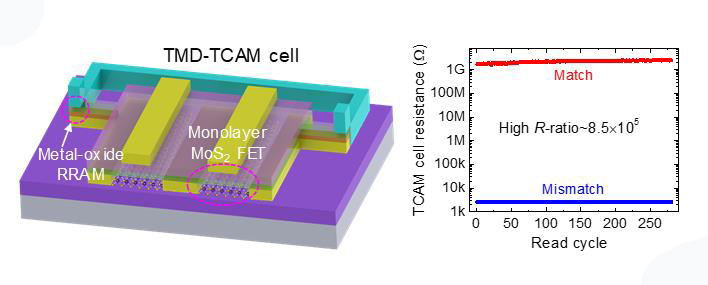

The integrated TCAM cells based on 2D transistors and RRAMs can enable parallel search of massive data with low energy consumption. Data in the figure are from paper Nature Electronics 2, 108-114 (2019).

The integrated TCAM cells based on 2D transistors and RRAMs can enable parallel search of massive data with low energy consumption. Data in the figure are from paper Nature Electronics 2, 108-114 (2019).

In the von Neumann computing architecture nowadays, the CPU and memory are usually separate from each other and are connected with wires or buses to transfer data. In data-intensive computation, the frequent off-chip memory access could result in up to 90% of the total latency and energy consumption. In-memory computing is promising for reducing the energy and delay because the data will be directly processed in the memory chip, which reduces the redundant data movement between the computation unit and the off-chip memory. TCAM is a powerful in-memory computing system for parallel search and pattern matching, and has been used in commercial products such as network routers. However, the current TCAMs usually have limited scale. TCAMs based on static random-access memories (SRAMs) have relatively high power consumption and relatively large TCAM cell size (~16 transistors per cell). Emerging resistive switching memories can be used in TCAMs instead because they are nonvolatile which reduces power consumption, and each TCAM cell only needs 2 transistors and 2 memories which decreases the cell size. Yet the resistance ratios (R-ratios) between the match and mismatch states have been reported to be around 100, which limits the search capacity.

In this collaborative work with Stanford University, Professor Rui Yang and collaborators have integrated the low-leakage monolayer MoS2 transistors with HfOx-RRAMs in a 2-transistor-2-resistor (2T2R) scheme to form the TCAM cell. Measurement results show a very large R-ratio between the match and mismatch states of up to 8.5×105, which is comparable with SRAM-based TCAM cells, with the key advantage that these 2T2R TCAM cells use far fewer transistors and have zero standby power by using non-volatile memories. These TCAM cells with large R-ratios can enable parallel search of massive data while maintaining enough sense margin, which can find a variety of applications including computing at the edge of the internet, multimedia processing, and big data analytics. The co-authors of this paper include Professor Philip Wong, Professor Eric Pop, Professor Jonathan Fan, Dr. Kirby Smithe, Dr. Taeho Kim, Dr. Kye Okabe, and Haitong Li from Stanford University. The research project is partly supported by the startup funding of the UM-SJTU Joint Institute.

Background Information

Rui Yang is a tenure-track Assistant Professor and Ph.D. advisor at the UM-SJTU Joint Institute. He obtained a Bachelor’s degree from Tianjin University in 2011, and a Ph.D. degree from Case Western Reserve University in 2016. From 2016 to 2018, he worked at Stanford University as a postdoctoral scholar. Professor Rui Yang joined JI in August 2018. His research group mainly focuses on RRAMs, NEMS, and 2D devices. He also serves as the Associate Editor of journal Micro & Nano Letters, and the Reviews Editor of journal Nanotechnology. In 2019, he was awarded sponsorship from the Shanghai Youth Science and Technology Talent Sailing Program by the Shanghai Municipal Science and Technology Commission.

Rui Yang is a tenure-track Assistant Professor and Ph.D. advisor at the UM-SJTU Joint Institute. He obtained a Bachelor’s degree from Tianjin University in 2011, and a Ph.D. degree from Case Western Reserve University in 2016. From 2016 to 2018, he worked at Stanford University as a postdoctoral scholar. Professor Rui Yang joined JI in August 2018. His research group mainly focuses on RRAMs, NEMS, and 2D devices. He also serves as the Associate Editor of journal Micro & Nano Letters, and the Reviews Editor of journal Nanotechnology. In 2019, he was awarded sponsorship from the Shanghai Youth Science and Technology Talent Sailing Program by the Shanghai Municipal Science and Technology Commission.